These are some nice article on verification, that I stumbled upon. Hope it will be useful for the reader

Some interesting article on Verification

Doing "cvs add" recursively

Those who are still stuck with the age-old CVS due to some unfortunate reason (in the age of Perforce ...), they must have encountered situations when they want to add multiple files/folders recursively. This is one command I found via google search which will help in such situation

.

find . -type d -print | grep -v CVS | xargs cvs add find . -type f -print | grep -v CVS | xargs cvs add

Writing SystemVerilog assertion for checking "setup/hold time violation" type of conditions

Recently, I gave couple of internal lectures on basic and advanced features of SystemVerilog assertion at the organization that I am working at. After that, quite a few colleague of mine have started asking questions on SVA. Amongst all, the most interesting assertion question is how to write assertion for checking "setup/hold time violation" type of scenarion. To understand these scenario, let's start with a very common example, which can be extended for many similar case.

Recently, I gave couple of internal lectures on basic and advanced features of SystemVerilog assertion at the organization that I am working at. After that, quite a few colleague of mine have started asking questions on SVA. Amongst all, the most interesting assertion question is how to write assertion for checking "setup/hold time violation" type of scenarion. To understand these scenario, let's start with a very common example, which can be extended for many similar case.Problem statement:

This is a standard problem, with not so easy solution of writing assertion for itWrite assertion for checking that the signal "data" is stable for tSetup time before positive edge of clock, and should be stable for tHold time after positive edge of clock. Here tSetup/tHold will be of static delay like 1ns, 30ps or so on. There are no extra inherent assumptions added with it (like clock period, its relationship with tSetup/tHold, or how fast the signal data can toggle.

In Verilog there is a way of checking it, which unfortunately is not an assertion, and hence can't be used with formal tools like Jasper. (via http://www.edaboard.co.uk/requesting-help-on-writing-sv-assertions-t442372.htmlhttp://www.edaboard.co.uk/requesting-help-on-writing-sv-assertions-t442372.html)

module timing_checks (input clk, en);

specify

specparam clk_high_time = 5;

specparam clk_low_time = 5;

$setup(en, negedge clk, clk_high_time * 4 / 5);

$hold(negedge clk, en, clk_low_time * 4 / 5);

endspecify

endmodule

Now let's proceed with assumption that we want to write an assertion for checking the same, we are not very much happy with $setup/$hold of Verilog. Here is the solution

module timing_checks_in_sv (input clk, data, ...);

...

event ev_data_delayed_toggled;

always @(data)

begin

fork

begin

# tSetup;

-> ev_data_delayed_toggled;

end

join_none

end

property setup_hold_time_checker;

time curr_time;

@(posedge clk) (1, curr_time = $time) |->

@(ev_data_delayed_toggled) (($time - curr_time) > (tSetup + tHold));

endproperty : setup_hold_time_checker

ASSERT_SETUP_HOLD: assert property setup_hold_time_checker;

endmodule

In the always block, we are triggering an event called ev_data_delayed_toggled, after tSetup time every time data toggles. Now the "setup/hold time" problem statement can be written as after posedge of clock, ev_data_delayed_toggled shouldn't get triggered within tSetup+tHold time. Now the problem statement has come to a form SVA timing check, which is specified in via the property.

There are many such not so intuitive, interesting use-case scenarios for SVA. Interested readers can have a look at the below link for some more interesting scenarios.

Labels: Assertion , System Verilog , Written by Subash

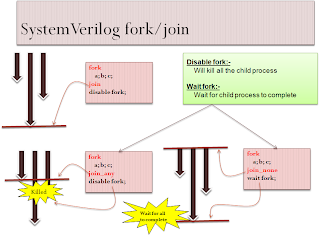

System Verilog Fine Grain Process Control - They are actually used in standard methodologies

Thanks to 2 articles in one Japanese blog, and google translate, I got to know that fine grain process control are use sparingly (mostly for process kill) in OVM/VMM. I am just pasting the link of these article in the hope that interested reader shall go through them, do some more research and get himself enlightened with the usage of fine grain process control of systemverilog.

- http://translate.googleusercontent.com/translate_c?hl=en&ie=UTF-8&sl=auto&tl=en&u=http://blogs.yahoo.co.jp/verification_engineer/59054470.html&prev=_t&rurl=translate.google.com&twu=1&usg=ALkJrhjOSZ0EoNcjjN0ZvudlDkX1QuY1Wg

- http://translate.googleusercontent.com/translate_c?hl=en&ie=UTF-8&sl=auto&tl=en&u=http://blogs.yahoo.co.jp/verification_engineer/59140597.html&prev=_t&rurl=translate.google.com&twu=1&usg=ALkJrhiVWUuHJqX6cjrKz5eHYaK3f_L8pg

Labels: fine grain process control , System Verilog

Advanced SystemVerilog Process Control – Beyond fork-join_X

always @(posedge req) begin

fork

begin : Label1

wait(a);

disable Label2;

end

begin : Label2

wait(b);

end

join

end

In the above mentioned code snippet, we are creating two threads named “Label1” and “Label2” at every posedge of req. In the thread “Label1”, as soon as signal “a” becomes HIGH, it kills the thread “Label2”.

In the above mentioned code snippet, we are creating two threads named “Label1” and “Label2” at every posedge of req. In the thread “Label1”, as soon as signal “a” becomes HIGH, it kills the thread “Label2”.But, there are few limitations in Verilog’s process creation, control as well as destruction. The main limitation of verilog’s fork-join statement is that there is very less flexibility in terms of when it should get out of fork loop. In addition, disabling of named block is not a good way of killing a process.

SystemVerilog solved the 1st limitation of verilog’s process control capabilities by adding new constructs like join_any, join_none, disable fork and wait fork. These constructs are widely used for controlling process creation/control/destruction.

However these constructs have further few limitations for finer control of process. Using the above constructs, we cannot suspend/resume/kill only a specific single process. SystemVerilog has a feature called “Fine grain process control” using which we can have much finer control on creation/control/destruction of process.

II. FINE GRAIN PROCESS CONTROL

Fine grain process control is meant for having finer control on processes compared to the control one can get using fork/join_x constructs. This is done using SystemVerilog’s inbuilt class called ’process’. Let’s look at the various feature of the above class and how to use them for finer control of processes.

A. Handle Creation and status check

To control any process/thread, we need to get the handle of the above thread using calling “process::self()” method of process class. Below code snippet will show how to do the same.

task abc(…);

process P;

process::state Pstate;

…

fork

begin

P = process::self();

…

Pstate = P.status();

end

join_none

endtask : abc

A process can be created for each always, initial block, and begin…end statement inside fork…join_X and dynamic processes. In addition, we can check the status of any process by calling status() method. A process can be in either of these 5 states (FINISHED, RUNNING, WAITING, SUSPENDED, KIL). “process::state” is a enumerated value and its content can be displayed using .name() method.

B. Process Suspension, Resumption, Await and Kill

Any process can be suspended or resumed by calling suspend() and resume() task of process class. Similarly, the process can be terminated by calling kill() method. The await() method blocks till the process is terminated. SystemVerilog code snippet given in section “USE-CASE: FINER CONTROL OF PROCESS”.

There can be few race conditions when a process is waiting for some event/variable change and we suspend the process. The question is on what condition the process shall resume its execution. These are simple rules to know when the process shall get unblocked from the waiting event[2]

- If the process is waiting for a delay like (#100 or #20ns) while going to suspend state, it will not count the time spent while in suspend state as the delay.

- If the process is waiting for an event (@(SV_event)) while going for suspend state, and the event has occurred when the process is at suspend state, then the process will be unblocked, and will start executing from the next while after resuming.

- If the process is waiting for variable change (@(SV_variable) or wait(SV_variable)) : Check for change of the variable is not performed when the process is suspended and hence any variable change happened during the time when the process is in suspended state shall not unblock the process if it is waiting for variable change and is put to suspend state

III. USE-CASE: PER-INSTANCE BASED FINER CONTROL OF PROCESSES.

Consider a scenario where we have created some N numbers of thread/process in one task. From another task, we want to suspend/resume/kill selected few tasks depending upon some other external conditions. Fine grain process control is extremely well suited for these kinds of tasks. Let see an example code snippet to understand how it can be done.

class fine_grain_process_ctrl_example;

// Data members

process p[20];

…

task spawn_thread;

for(int i=0; i<20; i++)

begin

fork

begin

p[i] = process::self();

run_thread();

end

join_none

end

endtask: spawn_thread

task control_thread;

…

// condition met for suspending p[i]

p[i].suspend();

…

// condition met for resuming p[j]

p[j].resume();

…

// condition met for killing p[k]

p[k].kill();

…

// Wait for completion of p[l]

p[l].await();

endtask: control_thread

endclass: fine_grain_process_ctrl_example

In the above code snippet, we have a class called fine_grain_process_ctrl, which has an array of process handles. In the task spawan_thread, where we are creating 20 parallel threads (by calling some external task run_thread()), we are also storing the handle of the process into the process array. Now in the task control_thread, we are controlling the suspension/resumption/termination of the above threads (which can be done in per-instance basis) depending upon some condition).

There is another advantage of the above way of doing the process control. Here effectively, we are de-coupling what to do in the thread, and how to handle thread. This decoupling is very useful for code-reuse. The details of the above aspect are described in more detail in next section.

IV. USE-CASE: DECOUPLING HOW AND WHEN

Consider a case where you have already written a transactor which sends packets according to your requirements. Now you need to change your code to make it work in the low-power-world where you need to stop sending packets whenever the system enters low-power state and resume sending packet once you are out of it. You have coded “HOW” to send your packet, and now you need to incorporate “WHEN” to send it, which itself can be far more complex that the simple “HOW”.

Consider a case where you have already written a transactor which sends packets according to your requirements. Now you need to change your code to make it work in the low-power-world where you need to stop sending packets whenever the system enters low-power state and resume sending packet once you are out of it. You have coded “HOW” to send your packet, and now you need to incorporate “WHEN” to send it, which itself can be far more complex that the simple “HOW”.You can directly go and modify the transactor code to incorporate “WHEN” aspect of the packet transmission. There are quite a few reasons why you would rather not touch the code and do the same in another way.

Fine grain process control can be very nicely used in such scenario. You can have a handle of the process of sending packet. Now using this handle, we can stop/resume execution of the process (thereby stopping/resuming sending of packet) by calling suspend/resume method. We can have another piece of code where we can code the logic which will have the logic that shall control “WHEN” to send the packet.

REFERENCES

[1] "IEEE Standard For SystemVerilog - Unified Hardware Design, Specification and Verification Language," IEEE Computer Society, IEEE, New York, NY, IEEE Std 1800-2009

[2] Article on “Fine Grain Process Control” at Synopsys Solvenet

System Verilog Fine Grain Process Control - Beyond SV LRM - Part I

There is exactly 1 and 1/2 page long section on "Fine grain process control" is SV LRM (along with not so easy to follow example). No wonder I have not seen much people using this nice feature of System Verilog. Fortunately Synopsys SolvNet has 3 nice article on it. I am listing them for reference. Hope it shall be useful to the reader. (NOTE : accessing these articles requires solvnet login, which I was told, is not so easy to obtain unless your organization has a vcs license, the truthfulness of which I have not yet verified)

| SN | Article Title |

| 1 | Fine Grain Process Control: Handle Creation & Status Check |

| 2 | Fine Grain Process Control: Process Await & Kill |

| 3 | Fine Grain Process Control: Process Suspend & Resume |

Labels: fine grain process control , System Verilog

Have you ever heard of a programming language called "Whitespace"?

The question of the day is "Have you ever heard of a programming language called Whitespace?". If the answer is no then please refer to wikipedia article on in. Quoting directly from wikipedia for the lazy ones who would rather like to stay at this page rather than visit the wikipedia site

Whitespace is an esoteric programming language developed by Edwin Brady and Chris Morris at the University of Durham (also developers of the Kaya programming language). It was released on 1 April 2003 (April Fool's Day). Its name is a reference to whitespace characters. Unlike most programming languages, which ignore or assign little meaning to most whitespace characters, the Whitespace interpreter ignores any non-whitespace characters. Only spaces, tabs and linefeeds have meaning.[1] An interesting consequence of this property is that a Whitespace program can easily be contained within the whitespace characters of a program written in another language, making the text a polyglot.[citation needed]

Next question that shall be naturally occurring to you, why am I posting a link of some arbit/useless language in a blog which is devoted to verification. To answer this, I shall begin by asking you to find out the error in this code. Assume x, y, z to be simple logic variable.

`define SWAP(__a, __b) \

__a = __a ^ __b; \

__b = __a ^ __b; \

__a = __a ^ __b;

...

`SWAP(x,y)

`SWAP(y,z)

...

Couldn't find any issue with it. Let me show the above example with white space character as [space].

`define SWAP(__a, __b) \

__a = __a ^ __b; \

__b = __a ^ __b; \[space]

__a = __a ^ __b;

...

`SWAP(x,y)

`SWAP(y,z)

...Now the issue is the extra white space character after \ of the SWAP macro definition. VCS doesn't like it and give some weird error which doesn't even tell that the error is due to the white-space after the \. I checked SV LRM and as per my understanding of reading the relevant section, it seems to be a valid system verilog code.

It took me half a day of banging my head in front of my monitor to find out that the issue is this extra whitespace after \ in the macro.

I feel Synopsys folks should do one of the following to make sure that no one else waste his precious time in debugging such hard-to-debug not-so-obvious issue.

- Ignore whitespce after \ in multi-line macro definition OR

- In case when a whitespace is encountered after \ in a multi-line macro, give error specifying that a whitespace character is encountered after \

What is Factory Pattern - v2.0

This post is a extended version of my original post on factory pattern which can be found at http://learn-systemverilog.blogspot.com/2009/08/what-is-factory-pattern.html

This post is a extended version of my original post on factory pattern which can be found at http://learn-systemverilog.blogspot.com/2009/08/what-is-factory-pattern.html

If you are working in System Verilog/VMM environment, it is high likely that you will be bombarded with word/expression from OOP world like "Factory Pattern", "Facade Pattern", "Observer Pattern" and so on. There is a finite possibility that you will seat down and start thinking what does those word mean and why they were used too frequently. Let me try to explain the idea/concept behind such word in the simplest way possible.

In SW engineering, a design pattern (or simply pattern) means a general repeatable solution to a commonly occurring problem. Most of these patterns have similarity to something or other in human society and hence they are known by that name.

Factory pattern as the name suggest, is aimed at solving the issue of creation of object. (Factory pattern is not the only pattern to deal with creation of objects, there are a bunch of more patterns for handling different kind of cases, and collectively they are known a creational patterns)

Let me give an example of case where we might need to use creational pattern and how to do so it in SV. Suppose you want to create a "Toy Factory" class which needs to create multiple types of toys (say toy aeroplane, toy tank, toy bus) depending upon the string input to it.

To create these different types of toys we need to have class defined for them. And there will be common method and data interface for these classes, hence it make sense to put all the common data member/task/functions in a class called toy class and then extend it.

class TOY;

// Common data memeber

string toy_name;

// Common methods

virtual function string get_type();

endclass : TOY

class TOY_Tank extends TOY;

function new();

this.toy_name = "Toy Tank";

endfunction : new

string function string get_type();

return this.toy_name;

endfunction : get_type

endclass : TOY_Tank

class TOY_Bus extends TOY;

function new();

this.toy_name = "Toy Bus";

endfunction : new

string function string get_type();

return this.toy_name;

endfunction : get_type

endclass : TOY_Bus

Now we are done with the bothering about the objects to be created. The next problem that we need to solve is to write the toy factory class itself. For simplicity, let's consider the case where we will want to pass 1 to get an instance of tank class and 2 for getting an instance of bus class from the factory. Now the factory class will look like this.

class TOY_factory;

Toy my_toy

// Common methods

function toy get_toy(string str);

if(str == "Toy Tank") this.my_toy = new TOY_Tank();

if(str == "Toy Bus") this.my_toy = new TOY_Bus();

return this.my_toy;

endfunction : get_toy

endclass : TOY_factoryNote that we are using virtual function for bringing polymorphism in action and save us from having an individual instance of the toy type in the factory class.

Reference

- Factory Method Design Pattern from sourcemaking.com

- Factory Method Pattern from wikipedia

- Factory Pattern from JAVA design pattern

Note

Mike Mintz has added the following word of caution/note for this in the thread http://verificationguild.com/modules.php?name=Forums&file=viewtopic&t=3763

The above link is very good. I would just like to add a word of caution. The factory pattern should be rather rare in your architecture. While the choice of where to put the "new" for a class is very important, most of the time (for big components) the answer is in the testbench. That's where all the drivers,generators,monitors, etc should be built.

Also the factory pattern is usually implemented as a function, not a class. When it's a class, you can get sloppy with the necessary parameters and you code is harder to follow.

I understand pretty well the warping of these cautions caused by the three letter methodologies and their misguided quest for generic components, so your usage may have to follow their guidelines. Just remember that (1) in the real world factory patterns are rare, and (2) you do not always have to do it the way the methodology says.

Labels: OOP , Pattern , Written by Subash

SystemVerilog-201x listening campaign - Brad are you still listening !!!

It seems recently the big guys in System Verilog (like Brad Pierce, just to give an idea of how big these guyz are) have decided to listen to people for possible improvement in System Verilog. The interested guy can check this page [http://bradpierce.wordpress.com/2009/12/14/systemverilog-201x-listening-campaign/] and give his/her "most likely" valuable comment and feel good about being a part of improving System Verilog to next level !!! (These kind of feel good are the only kind of feel good one can feel in these era of sub-prime induced recession, and similar economic artifacts) I have few idea/suggestion on improvement in SV to make it much more powerful/user friendly. I am listing them in the hope that someone might listen them and add them.

- The keyword “singleton” for defining a class as singleton object. It shall get rid of the need of some weird way of getting singleton class in SV

singleton class ABC; … endclass

- Unified verification methodology should be defined as a part of SV. There are way too many methodology now a days (like OVM, AVM, VMM and so on …). There should be one such standard methodology. It shall make life far easier for so many engineer.

- SV macros are a very powerful tool for reducing the amount of coding effort. SV improved quite a bit on verilog macro, but still there is a quite a bit scope for improvement. `` is a very rudimentary operator. It can’t be used for adding prefix to the input of the macro. See the hack that we need to do for adding prefix at http://learn-systemverilog.blogspot.com/2009/09/system-verilog-define-macros-why-and.html

`define PREFIX(__prefix, __name) __prefix“__name `define COV2(__name) `PREFIX(cp_,__name) : coverpoint __name {bins b = {1}; } // should be something like `define COV2(__name) cp_[[__name]] : coverpoint __name {bins b = {1}; } - There is scope for adding macro programming ability to SV. It should have the ability of generating code during macro processing phase.

`for(int i=0; i<12; i++) begin \ bind module_1 module_2 bind_mod_[[i]] (.*); \ end

- Ability to get signal by passing the hierarchical reference to the signal like wire a = get_signal(top.dut.abc.xyz);

- Option of crossing two cross coverage.

A : coverpoint ... B : coverpoint ... C : coverpoint ... D : coverpoint ... X : cross A, B; Y : cross C, D; // Z : cross X, Y; <----- SV doesn't allows it. It should

Free Timing Diagram Drawing tools

Many a times we need to generate/draw timing diagrams for multitude purposes. While browsing web for the same I came across these free/easy-to-use timing diagram drawing utilities.

- Timing Diagram Font -- Timing diagram can be generated in MS Word using this

- Timing Analyzer -- A tool for doing the same

- Timing Diagram from verilog - using the above tool and small snippet of verilog code, one can generate timing waveform from the design itself. One problem I see with it is that the code snippet doesn't use verilog macro for achieving the same.

- Handy Timer - A simple and handy timing diagram editor

- Timing Editor - Another free waveform editor

- Draw Timing - Command line based waveform drawing SW which take a script as its input

Labels: timing diagram , Tools